if id rf exe mem wb IF and ID Stages. Instruction Fetch. Get the next instruction from memory. Increment Program . $26.49

0 · mem and wb stages

1 · if mem and wb steps

2 · if and id wb

$18.99

A set of registers (IF/ID, ID/EX, EX/MEM, MEM/WB) is placed between each pipe stage. used .IF and ID Stages. Instruction Fetch. Get the next instruction from memory. Increment Program .

IF and ID Stages. Instruction Fetch. Get the next instruction from memory. Increment Program .IF ID/RF EX MEM WB • Read After Write (RAW) Instr Jtries to read operand before Instr .

In summary, in the design I've discussed, the sizes of intermediate registers are .• RF–instruction decode and register fetch, hazard checking and also instruction cache hit .

Stage 2: Instruction Decode. On every cycle: Read IF/ID pipeline register to get instruction bits. .Steps in processing an instruction: Instruction Fetch (IF_STEP) Instruction Decode (ID_STEP) .

IF and ID Stages. 1. Instruction Fetch. » Get the next instruction from memory. » Increment Program Counter value by 4. 2. Instruction Decode. » Figure out what the instruction says to do. » Get values from the named registers. » Simple instruction format means we know which registers we may need before the instruction is fully decoded.

In other words, the main units are idle for most of the 8ns cycle! — The instruction RAM is used for just 2ns at the start of the cycle. — Registers are read once in ID (1ns), and written once in WB (1ns). — The ALU is used for 2ns near the middle of the cycle. — Reading the data memory only takes 2ns as well.A set of registers (IF/ID, ID/EX, EX/MEM, MEM/WB) is placed between each pipe stage. used to save instruction state as it propagates through the pipe. instructions are only active in one pipe stage at a time. inter-stage registers are master-slave D .IF and ID Stages. Instruction Fetch. Get the next instruction from memory. Increment Program Counter value by 4. Instruction Decode. Figure out what the instruction says to do. Get values from the named registers. Simple instruction format means we know which registers we may need before the instruction is fully decoded. 4.IF and ID Stages. Instruction Fetch. Get the next instruction from memory. Increment Program Counter value by 4. Instruction Decode. Figure out what the instruction says to do. Get values from the named registers. ec. 4. EX, MEM, and WB stages. 3. Execute. On a memory reference, add up base and offset. hm.

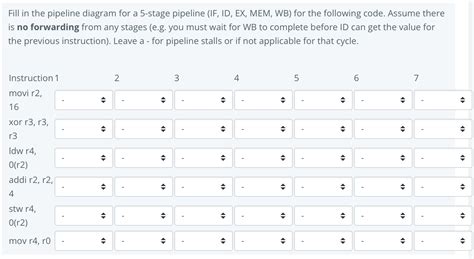

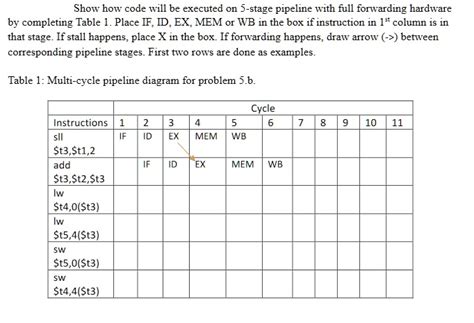

IF ID/RF EX MEM WB • Read After Write (RAW) Instr Jtries to read operand before Instr Iwrites it • Caused by a “Dependence” (in compiler nomenclature). This hazard results from an actual need for communication. Three Generic Data Hazards I: add r1,r2,r3 J: sub r4,r1,r3 • Write After Read (WAR) InstrJwrites operand before InstrI reads it

ez100pr pcsc smart card reader driver

mem and wb stages

In summary, in the design I've discussed, the sizes of intermediate registers are as follows: IF/ID is 8 bytes in size, ID/EX is 20 bytes in size, EX/MEM is 25 bits in size, and MEM/WB is 8 bytes in size.• RF–instruction decode and register fetch, hazard checking and also instruction cache hit detection. • EX–execution, which includes effective address calculation, ALU

Stage 2: Instruction Decode. On every cycle: Read IF/ID pipeline register to get instruction bits. Decode instruction, generate control signals. Read from register file. Write values of interest to pipeline register (ID/EX) Control information, Rd index, immediates, offsets, .Steps in processing an instruction: Instruction Fetch (IF_STEP) Instruction Decode (ID_STEP) Operand Fetch (OF_STEP) Might be from registers or memory. Execute (EX_STEP) Perform computation on the operands.IF and ID Stages. 1. Instruction Fetch. » Get the next instruction from memory. » Increment Program Counter value by 4. 2. Instruction Decode. » Figure out what the instruction says to do. » Get values from the named registers. » Simple instruction format means we know which registers we may need before the instruction is fully decoded.

In other words, the main units are idle for most of the 8ns cycle! — The instruction RAM is used for just 2ns at the start of the cycle. — Registers are read once in ID (1ns), and written once in WB (1ns). — The ALU is used for 2ns near the middle of the cycle. — Reading the data memory only takes 2ns as well.

A set of registers (IF/ID, ID/EX, EX/MEM, MEM/WB) is placed between each pipe stage. used to save instruction state as it propagates through the pipe. instructions are only active in one pipe stage at a time. inter-stage registers are master-slave D .IF and ID Stages. Instruction Fetch. Get the next instruction from memory. Increment Program Counter value by 4. Instruction Decode. Figure out what the instruction says to do. Get values from the named registers. Simple instruction format means we know which registers we may need before the instruction is fully decoded. 4.IF and ID Stages. Instruction Fetch. Get the next instruction from memory. Increment Program Counter value by 4. Instruction Decode. Figure out what the instruction says to do. Get values from the named registers. ec. 4. EX, MEM, and WB stages. 3. Execute. On a memory reference, add up base and offset. hm.

IF ID/RF EX MEM WB • Read After Write (RAW) Instr Jtries to read operand before Instr Iwrites it • Caused by a “Dependence” (in compiler nomenclature). This hazard results from an actual need for communication. Three Generic Data Hazards I: add r1,r2,r3 J: sub r4,r1,r3 • Write After Read (WAR) InstrJwrites operand before InstrI reads it In summary, in the design I've discussed, the sizes of intermediate registers are as follows: IF/ID is 8 bytes in size, ID/EX is 20 bytes in size, EX/MEM is 25 bits in size, and MEM/WB is 8 bytes in size.

• RF–instruction decode and register fetch, hazard checking and also instruction cache hit detection. • EX–execution, which includes effective address calculation, ALU

Stage 2: Instruction Decode. On every cycle: Read IF/ID pipeline register to get instruction bits. Decode instruction, generate control signals. Read from register file. Write values of interest to pipeline register (ID/EX) Control information, Rd index, immediates, offsets, .

if mem and wb steps

ez mini smart card reader driver

Award. Share. Epikgamer332. • 1 yr. ago. NFC isn't located in the joystick, rather, in front of the .

if id rf exe mem wb|if and id wb